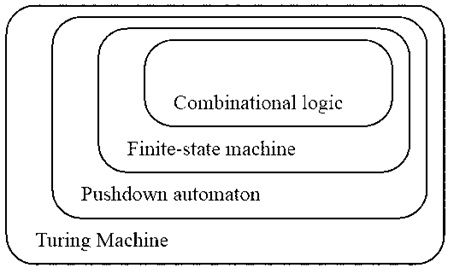

کی بنیادی خرابی مشترکہ سرکٹ یہ موجودہ اور پچھلی ریاستوں کو بچانے کے لئے کوئی میموری استعمال نہیں کرتا ہے۔ لہذا ان پٹ کی سابقہ حالت سرکٹ کی موجودہ حالت پر کوئی اثر نہیں ڈالتی ہے۔ جبکہ ، ترتیب والے سرکٹ میں میموری ہوتی ہے لہذا ان پٹ کی بنیاد پر آؤٹ پٹ مختلف ہوسکتی ہے۔ اس قسم کے سرکٹس میں پچھلے ان پٹ ، آؤٹ پٹ ، گھڑی اور میموری عنصر کا استعمال ہوتا ہے۔ یہاں میموری عناصر لچ یا پلٹ فلاپ ہوسکتے ہیں۔ سیکوئینشل سرکٹس کو مختلف طریقوں سے تیار کیا گیا ہے جیسے ROM اور flips ، PLAs ، سی پی ایل ڈی (کمپلیکس پروگرام قابل منطق ڈیوائس) ، ایف پی جی اے (فیلڈ پروگرام قابل گیٹ گیٹ صف) . اس آرٹیکل میں ، ہم صرف اس پر تبادلہ خیال کرنے جارہے ہیں کہ پی ایل اے کا استعمال کرتے ہوئے ترتیب وار سرکٹ کو کس طرح ڈیزائن کیا جائے۔

جیسا کہ ذیل میں دکھایا گیا ہے سلسلہ وار سرکٹ کا بلاک ڈایاگرام:

سلسلہ وار سرکٹ کا بلاک ڈایاگرام

PLAs کا استعمال کرتے ہوئے ترتیب وار سرکٹ کی ڈیزائننگ

ترتیب وار سرکٹس پی ایل اے (پروگرام لائق لاجک اریز) اور پلٹ فلاپس کا استعمال کرتے ہوئے محسوس کیا جاسکتا ہے۔ اس ڈیزائن میں ، ریاست کی تفویض اہم ہوسکتی ہے کیونکہ اچھے ریاستی اسائنمنٹ کا استعمال مصنوعات کی شرائط کی مطلوبہ تعداد کو کم کرسکتا ہے اور ، لہذا پی ایل اے کے مطلوبہ سائز کو کم کرسکتا ہے۔ پروڈکٹ کی اصطلاح جو لفظی جمع کے طور پر بیان کی جاتی ہے ، جہاں ہر لفظی یا تو متغیر ہوتا ہے یا اس کی نفی۔

آئیے ہمیں ڈیزائن کوڈ کنورٹر پر غور کریں۔ نیچے دیئے گئے ریاستی ٹیبل کو ایک پی ایل اے اور تین کا استعمال کرکے محسوس کیا جاسکتا ہے پلٹائیں جیسا کہ اعداد و شمار کے نیچے دکھایا گیا ہے یہ سرکٹ کنفیگریشن ROM فلپ فلاپ پر مبنی ڈیزائن سے بہت ملتی جلتی ہے ، سوائے اس کے کہ ROM کو مناسب سائز کے PLA نے تبدیل کیا ہے۔ ریاست کی تفویض ذیل میں دی گئی سچائی میز کی طرف لے جاتی ہے۔ اس ٹیبل کو پی ایل اے میں چار ان پٹ ، 13 مصنوعات کی شرائط ، اور چار آؤٹ پٹ کے ساتھ اسٹور کیا جاسکتا ہے ، لیکن یہ 16 الفاظ والے روم کے مقابلے میں سائز میں تھوڑا سا کم پیش کش کرے گا۔

| X Q1 Q2 Q3 | ڈی 1 ڈی 2 ڈی 3 کے ساتھ |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 ایکس ایکس ایکس ایکس 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 ایکس ایکس ایکس ایکس ایکس ایکس ایکس ایکس |

ٹیبل: حقیقت ٹیبل

موجودہ حالت

| اگلی ریاست ایکس = 0 1 | موجودہ آؤٹ پٹ (زیڈ) |

| TO | بی سی | 1 0 |

بی سی | ڈی ای اور ای | 1 0 0 1 |

ڈی ہے | H H H M | 0 1 1 0 |

H ایم | A A TO - | 0 1 1 - |

ٹیبل: اسٹیٹ ٹیبل

پی ایل اے کا استعمال کرتے ہوئے ترتیب وار سرکٹس کی ڈیزائننگ

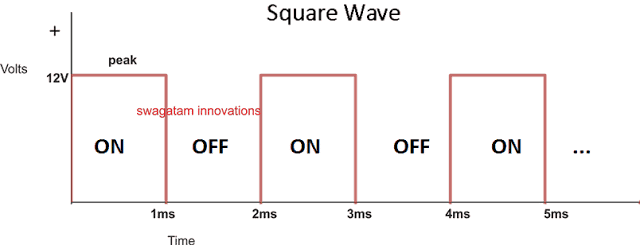

ان پٹ آؤٹ پٹ مساوات کارنو نقشہ کے ذریعے اخذ کردہ

یہاں ، چونکہ سات ریاستیں ہیں ، تین ڈی فلپ فلاپس کی ضرورت ہے۔ اس طرح ، 4 ان پٹ اور 4 آؤٹ پٹ کے ساتھ پی ایل اے سرکٹ کی ضرورت ہے۔ اگر کوڈ کنورٹر کی ریاستی تفویض پر غور کیا جائے تو ، نتیجہ کے نتیجے میں آؤٹ پٹ مساوات اور کرنف سے ماخوذ ڈی فلپ فلاپ ان پٹ مساوات کو درج ذیل مساوات لکھے جاسکتے ہیں۔

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X 'Q1 Q3' = X Q1 'Q2'

زیڈ = ایکس 'کیو 3' + ایکس کیو 3

| X Q1 Q2 Q3 | ڈی 1 ڈی 2 ڈی 3 کے ساتھ |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 گیارہ

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

پی ایل اے ٹیبل جو ان مساوات سے مطابقت رکھتا ہے ، مندرجہ بالا ٹیبل میں دیا گیا ہے۔ اس ٹیبل کو پی ایل اے کا استعمال کرکے چار ان پٹ ، سات پروڈکٹ شرائط ، اور چار آؤٹ پٹس حاصل کیے جاسکتے ہیں۔ ابتدائی طور پر مذکورہ ڈیزائن کے کام کی تصدیق کے ل ass ، فرض کریں کہ X = 0 اور Q1Q2Q3 = 000۔ اس نے قطار میں - - 0- اور 0 - - -0 کو ٹیبل میں منتخب کیا ، لہذا Z = 0 اور D1D2D3 = 100۔ فعال گھڑی کے کنارے کے بعد ، Q1Q2Q3 = 100۔ اگر اگلی ان پٹ X = 1 ہے ، تو پھر قطاریں - - 0 - اور - 1- - منتخب کی گئی ہیں ، لہذا Z = 0 اور D1D2D3 = 110 ہے۔ فعال گھڑی کے کنارے کے بعد ، Q1Q2Q3 = 110۔

قابل پروگرام منطق سرنی (PLA)

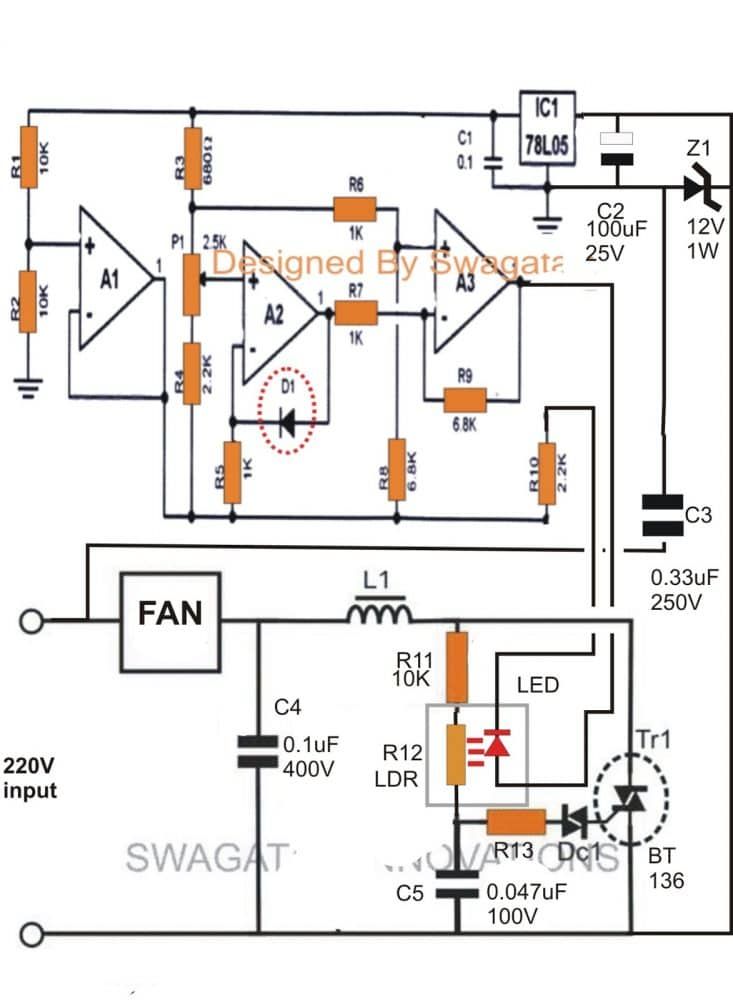

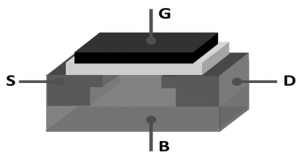

پروگرام لائق منطق کا صفی ایک قابل پروگرام منطقی آلہ ہے۔ یہ عام طور پر مشترکہ منطق کے سرکٹس کو نافذ کرنے کے لئے استعمال کیا جاتا ہے۔ پی ایل اے میں پروگرام قابل اور طیاروں (اور سرنی) کا ایک سیٹ ہے ، جو پروگرام کے قابل یا طیاروں (یا سرنی) کے سیٹ سے منسلک ہوتا ہے ، جس کے بعد آؤٹ پٹ تیار کرنے کے لئے اسے مکمل طور پر تکمیل کیا جاسکتا ہے۔ اس لے آؤٹ میں بڑی تعداد میں منطقی افعال کو ترکیب میں بننے کی اجازت دیتا ہے مصنوعات کا مجموعہ (SOP) روایتی شکلیں۔ ایک پی ایل اے کا ایک عام بلاک ڈایاگرام ذیل میں دیا گیا ہے۔

PLA کا بلاک ڈایاگرام

پی ایل اے اور پال (پروگرام قابل سرنی منطق) کے درمیان بنیادی فرق یہ ہے ،

پی ایل اے: دونوں اور ہوائی جہاز اور OR ہوائی جہاز کرمادیش ہیں۔

پال: صرف اور ہوائی جہاز قابل پروگرام ہے ، جبکہ OR طیارہ طے شدہ ہے۔

پی ایل اے کی بہتر تفہیم کے ل here ، ہم یہاں ذیل کی مثال پر غور کر رہے ہیں۔

آئیے ان تقریب F1 اور f2 کو نافذ کرنے کی کوشش کرتے ہیں

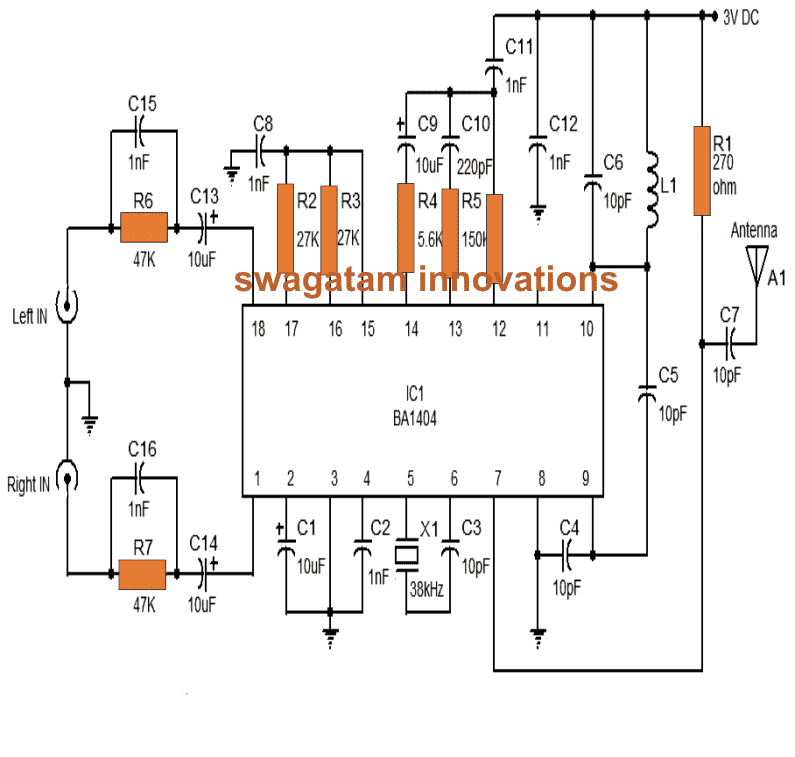

ان پٹ ایکس 1 ، ایکس 2 ، ایکس 3 اور ان سے متعلقہ تکمیل شدہ اشارے پروگرام اور قابل طیارے کو دیئے جاتے ہیں ، وہاں ہمیں P1 ، P2 ، P3 کالڈ منٹرس کے بطور جہاز اور آؤٹ پٹ ملیں گے۔ پھر یہ اشارے مطلوبہ آؤٹ پٹ فنکشن F1 اور F2 (مصنوعات کا مجموعہ) تیار کرنے کے لئے پروگرام ایبل یا ہوائی جہاز کو دیئے جاتے ہیں۔ مندرجہ ذیل اعداد و شمار دیئے گئے فعالیت کیلئے پی ایل اے کے گیٹ لیول پر عمل درآمد کو بیان کرتے ہیں۔

پی ایل اے کا نفاذ

یہ سب PLA کا استعمال کرتے ہوئے ترتیب وار سرکٹس کی ڈیزائننگ کے بارے میں ہے۔ ہم غور کرتے ہیں کہ اس مضمون میں دی گئی معلومات آپ کو اس تصور کی بہتر تفہیم کے لئے مددگار ثابت ہیں۔ مزید برآں ، اس مضمون کے بارے میں کوئی سوالات یا اس میں کوئی مدد بجلی اور الیکٹرانکس کے منصوبوں کو نافذ کرنا ، آپ نیچے تبصرہ سیکشن میں تبصرہ کرکے ہم سے رابطہ کرسکتے ہیں۔ آپ کے لئے ایک سوال یہ ہے ، ایک ترتیب سرکٹ سے کیا مراد ہے؟